| Prev | Next |

StateMachine Modeling For HDLs

To efficiently generate Hardware Description Language (HDL) code from StateMachine models, apply the design practices described in this topic. Hardware Description Languages include VHDL, Verilog and SystemC.

In an HDL StateMachine model, you might expect to:

- Designate Driving Triggers

- Establish Port–Trigger Mapping

- Add to Active State Logic

Operations

Operation |

Description |

See also |

|---|---|---|

|

Designate Driving Triggers |

|

State Machine Diagrams Trigger |

|

Establish Port-Trigger Mapping |

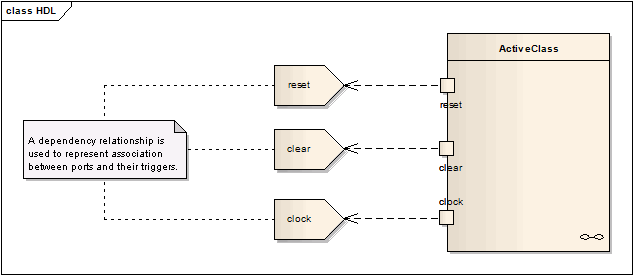

After successfully modeling the different operating modes of the component, and the Triggers associated with them, you must associate the Triggers with the component's Ports. A Dependency relationship from the Port to the associated Trigger is used to signify that association.

|

|

|

Active State Logic |

Designating the driving Trigger and establishing the Port-Trigger mapping put in place the preliminaries required for efficiently interpreting the hardware components. The actual StateMachine logic is now modeled within the Active (SubMachine) state. |

Notes

Learn more